-

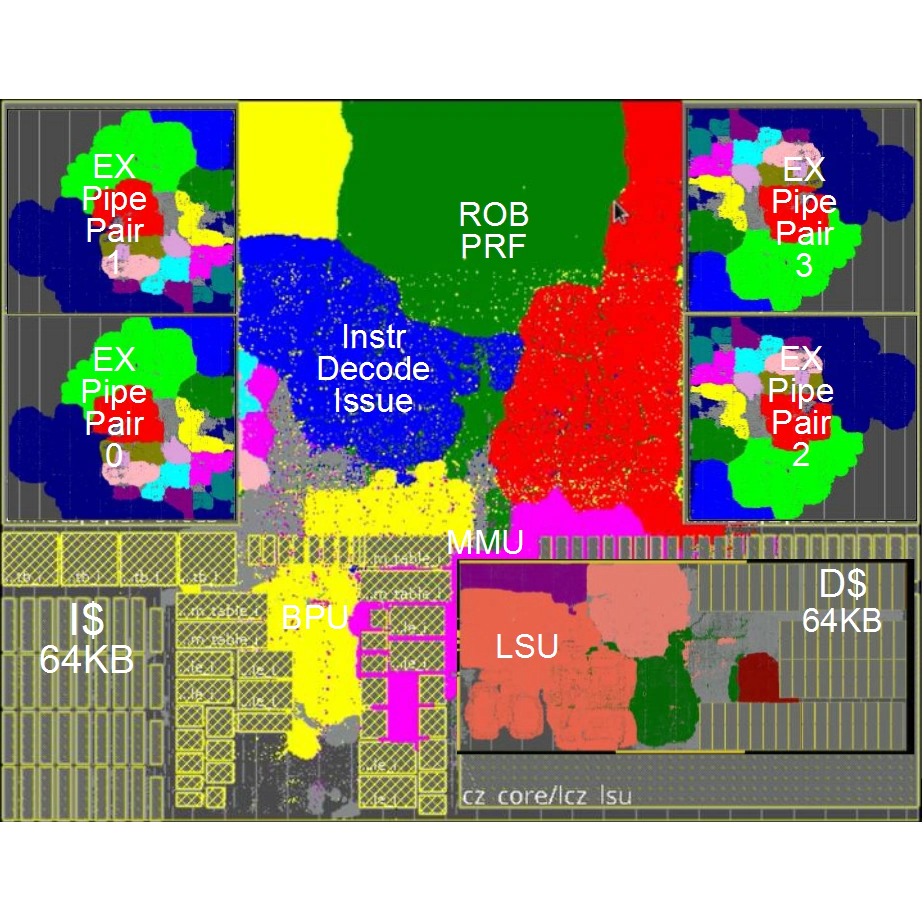

RISC-V Startup Condor Computing’s Cuzco Core Takes Flight

Condor Computing’s new Cuzco RISC-V core uses novel time-based instruction issuing, reducing power and area by eliminating CAM circuits and instruction replays. It’s a major microarchitectural innovation that exemplifies the opportunities the open RISC-V architecture fosters. continue reading

-

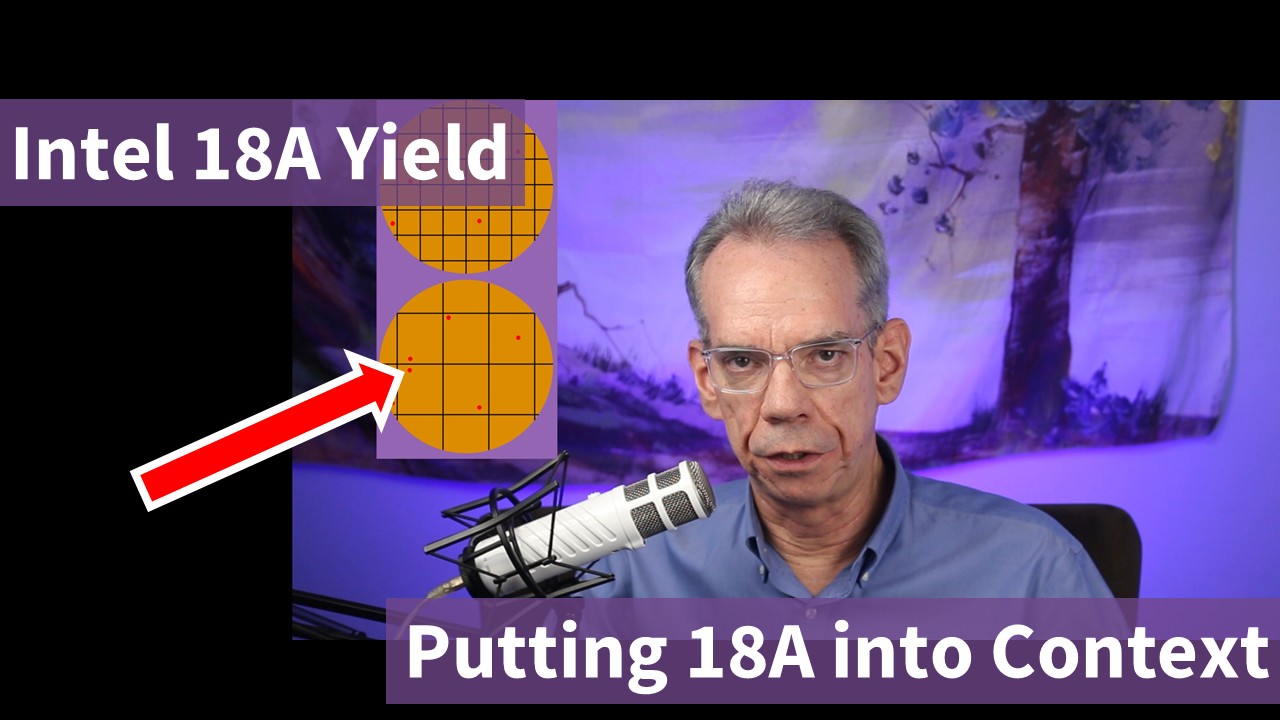

Let’s Talk About Intel 18A Yield Rumors

This video discusses reports that have surfaced indicating that Intel 18A has poor yields. continue reading

-

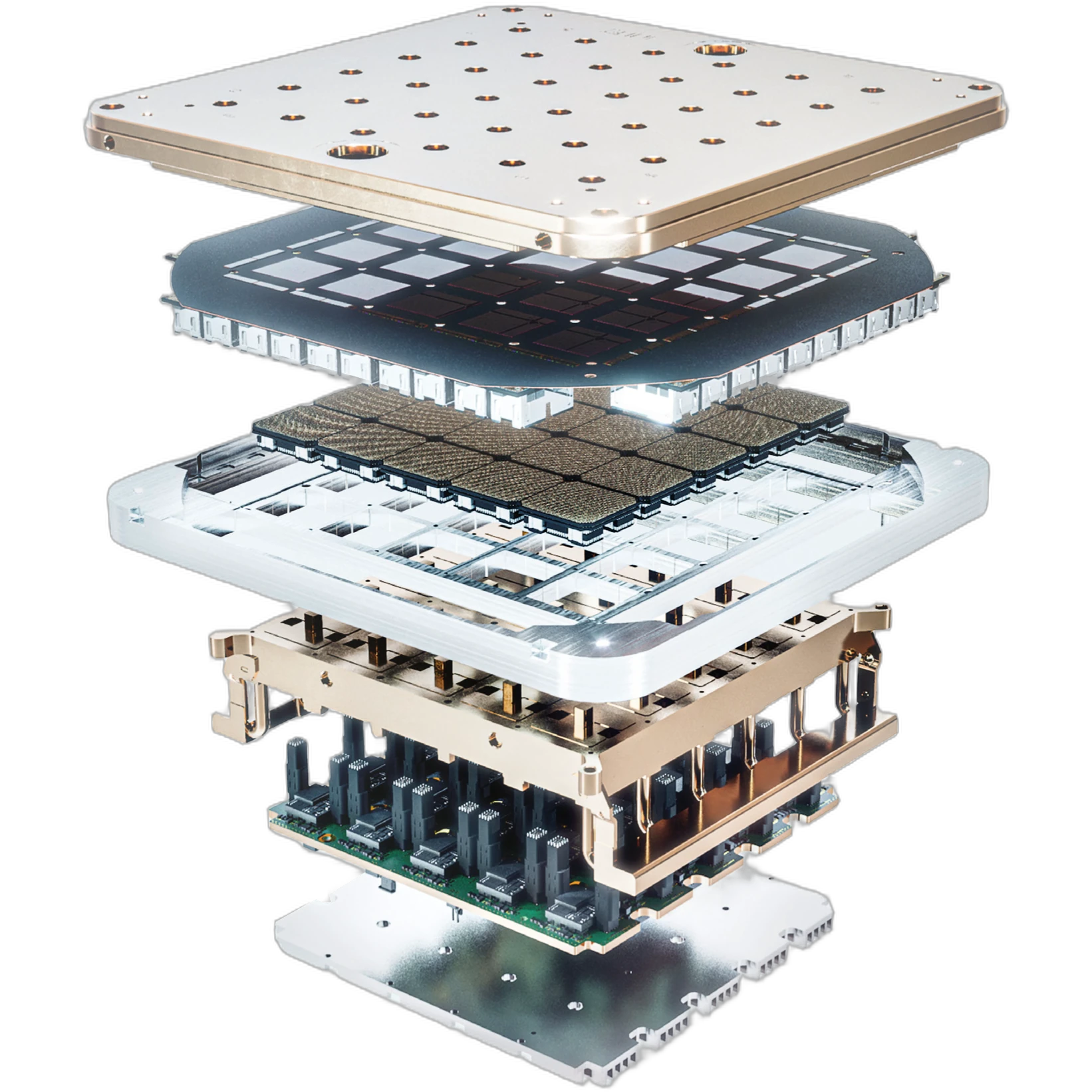

Tesla Dojo Loses Mojo

Four years after disclosing its D1 AI accelerator (NPU), the heart of its Dojo system, electric-car company Tesla has pulled the plug. After unveiling the D1, the company touted grand plans, promising in July 2023, when it began Dojo production (a year after the initial public target), that it will have deployed enough computing capacity… continue reading

-

What Would 100% Semiconductor Tariffs Mean?

The US proposes a 100% semiconductor tariff on imports. Details are unclear, but it could hit some unexpected countries. continue reading

Popular

Sponsored Content and Plugs

- Ceva Boosts NeuPro-M NPU Throughput and Efficiency

- Slash Server Costs Without Hardware or Software Changes

- MEXT Helps IT Leaders Find the Sweet Spot

- Chips Act Backs Chiplets

- Arteris Expands NoC Offerings for AI Accelerators

Other Sites You Might Like

Read More

AMD Apple APU/IGP Arm auto Broadcom Ceva CPU data center DPU DSP edge AI embedded Enfabrica Epyc FPGA Google GPU Imagination Intel Marvell MCU MediaTek memory Meta Microsoft MLPerf networking NPU (AI accelerator) Nvidia NXP OpenAI PC policy process tech Qualcomm RISC-V SambaNova SiFive smartphone SoftBank software Tenstorrent Tesla Untether